# PCI-1742U

# 16-bit, 1MS/s High-Resolution Multifunction Card

# **Packing List**

Before installation, please make sure that you have received the following:

- PCI-1742U DA&C card

- Driver CD

- · Quick Start User Manual

If anything is missing or damaged, contact your distributor or sales representative immediately.

#### **User Manual**

For more detailed information on this product, please refer to the PCI-1742U User Manual on the CD-ROM (PDF format).

CD:\Documents\Hardware Manuals\PCI\PCI-1742U

## **Declaration of Conformity**

#### FCC Class A

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause interference in which case the user is required to correct interference at his own expense.

#### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### Overview

The PCI-1742U is a powerful high-resolution multifunction DAS card with 1MS/s sampling rate and 16-bit resolution, fulfills the needs of most data acquisition applications. PCI-1742U provides 16 single-ended or 8 differential analog input channels, two 16-bit D/A output channels, 16 digital input/output channels, and one 10 MHz 16-bit counter channel.

#### **Notes**

For more information on this and other Advantech products, please visit our websites at:

http://www.advantech.com/eAutomation

For technical support and service:

http://www.advantech.com/support/

This startup manual is for PCI-1742U.

Part No. 2003174210

1st Edition

May 2007

# **Specifications**

#### **Analog Input**

| Analog Input  |                                             |         |         |        |         |        |

|---------------|---------------------------------------------|---------|---------|--------|---------|--------|

| Channels      | 16 single-ended or 8 differential or combi- |         |         |        |         |        |

|               | nation                                      |         |         |        |         |        |

| Resolution    | 16-bit                                      |         |         |        |         |        |

| FIFO Size     | 1K samp                                     |         |         |        |         |        |

| Max. Sampling |                                             |         |         |        |         |        |

| Rate          | 800kS/s                                     |         |         |        |         |        |

|               | 250kS/s                                     |         |         |        |         |        |

| A/D converter | Normal i                                    | mode:   | maxim   | ium 80 | 00kS/s  | mini-  |

| mode          | mum: no                                     | )       |         |        |         |        |

|               | Warp mo                                     | ode: m  | aximu   | m 1MS  | s/s min | imum:  |

|               | 1kS/s                                       |         |         |        |         |        |

| Input range   | PGA                                         | 0.5     | 1       | 2      | 4       | 8      |

| and           | Gain                                        |         |         |        |         |        |

| PGA Gain List | Unipolar                                    | N/A     | 0~10    | 0~5    |         | 0~1.25 |

|               | Bipolar                                     |         | ±5      | ±2.5   |         | ±0.625 |

| Bandwidth of  |                                             | 0.5     | 1       | 2      | 4       | 8      |

| PGA           | Gain                                        |         |         |        |         |        |

|               |                                             | 2MHz    | 2MHz    | 1MHz   | 1MHz    | 800kHz |

|               | width                                       |         |         |        |         |        |

| Common Mode   | ±7 V ma                                     | х. (оре | eration | al)    |         |        |

| Voltage       |                                             |         |         |        |         |        |

| Protection    | ±20 V                                       |         |         |        |         |        |

| Input         | 100 M/10pF(Off); 100 M/100pF(On)            |         |         |        |         |        |

| Impedance     |                                             |         |         |        |         |        |

| Accuracy      | DCDNLE: ±1LSB                               |         |         |        |         |        |

|               | INLE: ±3LSB                                 |         |         |        |         |        |

|               | Offset error: Adjustable to ±2 LSB          |         |         |        |         |        |

|               | Gain                                        |         |         | 2      | 4       | 8      |

|               | Gain                                        |         | .02 0.0 | 0.0    | 2 0.03  | 0.04   |

|               | error                                       |         |         |        |         |        |

|               | (% F                                        |         |         | L      |         |        |

|               | ACTHD: -90 dB                               |         |         |        |         |        |

|               | ENOB: 13.5 bits @ 1MS/s 14.5 bits @         |         |         |        |         |        |

|               | < 250KS/s                                   |         |         |        |         |        |

# **Analog Output**

| Channels      | 10                           |                                    |  |

|---------------|------------------------------|------------------------------------|--|

|               | 2                            |                                    |  |

| Resolution    | 16-bit                       |                                    |  |

| Throughput    | 2MS/s max. per channel (FSR) |                                    |  |

|               |                              | . ,                                |  |

|               |                              |                                    |  |

| O             |                              | 0 .51/ 0 .401/                     |  |

| Output        | Using                        | 0~+5V, 0~+10 V,                    |  |

| Range (Inter- | Internal                     | -5~+5V,-10~+10V                    |  |

| nal & `       | Reference                    |                                    |  |

| External      | Using                        | 0~+x V@ +x V (-10 x 10)            |  |

|               | External                     | -x~+x V@ +x V (-10 x 10)           |  |

| Reference)    |                              |                                    |  |

| _             | Reference                    |                                    |  |

| Accuracy      | DC                           | DNLE: ±1LSB (monotonic)            |  |

|               |                              | INLE: ±2LSB                        |  |

|               |                              | IINLE: ±2LSB                       |  |

|               |                              | Offset error: Adjustable to ±2 LSB |  |

|               |                              | Gain error: Adjustable to ±2 LSB   |  |

|               |                              | •                                  |  |

| Dynamic       | Settling                     | 0.5µs (to 4 LSB of FSR)            |  |

| Performance   | Time                         |                                    |  |

|               | Slew Rate                    | 40 V/us                            |  |

|               |                              | 10 17μ0                            |  |

| Driving       | ±2mA                         |                                    |  |

| Capability    |                              |                                    |  |

| Output        | 2.5 ohm                      |                                    |  |

| Impedance     |                              |                                    |  |

| Tempco        | Gain: 30 p                   | nm/°C                              |  |

|               | Offset: 15                   |                                    |  |

|               | Oliset: 15                   | 1V/ C                              |  |

### **Specifications**

#### Digital Input /Output

| Input channels   | 16   |                            |

|------------------|------|----------------------------|

| Output channels  | 16   |                            |

| Number of ports  | 2    |                            |

| Input Voltage    | Low  | 0.8 V max.                 |

|                  | High | 2.0 V min.                 |

| Output Voltage   | Low  | 0.5 V max.@+24 mA (sink)   |

|                  | High | 2.4 V min.@-15 mA (source) |

| Pull up resistor | 10k  |                            |

#### Counter/Timer

| Channels     | 1 (82C54)  |

|--------------|------------|

| Resolution   | 16-bit     |

| Clock source | 10MHz max. |

| Clock Tempco | 50 ppm/°C  |

#### General

| I/O Connector Type | 68-pin SCSI-II female                                      |                                                      |  |

|--------------------|------------------------------------------------------------|------------------------------------------------------|--|

| Dimensions         | 175 × 100 mm (6.9" × 3.9")                                 |                                                      |  |

| Power Consumption  | Typical                                                    | +5 V @ 850 mA<br>+12 V @ 600 mA                      |  |

|                    | Max.                                                       | +5 V @ 1 A<br>+12 V @ 700m A                         |  |

| Temperature        | Operation                                                  | 0~+60°C (32~158°F)<br>(refer to <i>IEC 68-2-1,2)</i> |  |

|                    | Storage                                                    | -20~+85°C (-4~185°F)                                 |  |

| Relative Humidity  | 5 ~ 95% RH non-condensing<br>(refer to <i>IEC 68-2-3</i> ) |                                                      |  |

| Certification      | CE certified                                               |                                                      |  |

#### Installation

#### **Software Installation**

#### **Hardware Installation**

- 1. Turn off your computer and unplug the power cord and cables. Turn off your computer before installing or removing any components.

- 2. Remove the cover of your computer.

- Remove the slot cover on the back panel of your computer.

- Touch the metal part on the surface of your computer to neutralize any static electricity that might be in your body.

- Insert the PCI-1742U card into a PCI slot. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided; or the card might be damaged.

- 6. Fasten the bracket of the PCI card on the back panel rail of the computer with screws.

- Connect appropriate accessories (68-pin cable, wiring terminals, etc. if necessary) to the PCI card.

- Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- 9. Plug in the power cord and turn on the computer.

# Pin Assignment

|   |      |    |        | ı    |

|---|------|----|--------|------|

|   | AI0  | 68 | <br>34 | AI1  |

|   | AI2  | 67 | 33     | AI3  |

|   | AI4  | 66 | 32     | AI5  |

|   | AI6  | 65 | 31     | AI7  |

|   | AI8  | 64 | 30     | AI9  |

|   | AI10 | 63 | 29     | AI11 |

|   | AI12 | 62 | 28     | AI13 |

|   | AI14 | 61 | 27     | AI15 |

| A | GND. | 60 | 26     | AGNI |

|   | AI16 | 59 | 25     | AI17 |

|   | AI18 | 58 | 24     | AI19 |

|   | AI20 | 57 | 23     | AI21 |

|   | AI22 | 56 | 22     | AI23 |

|   | AI24 | 55 | 21     | AI25 |

|   | AI26 | 54 | 20     | AI27 |

|   | AI28 | 53 | 19     | AI29 |

|   | AI30 | 52 | 18     | AI31 |

|   | AI32 | 51 | 17     | AI33 |

|   | AI34 | 50 | 16     | AI35 |

|   | AI36 | 49 | 15     | AI37 |

|   | AI38 | 48 | 14     | AI39 |

|   | AI40 | 47 | 13     | AI41 |

|   | AI42 | 46 | 12     | AI43 |

|   | AI44 | 45 | 11     | AI45 |

|   | AI46 | 44 | 10     | AI47 |

| A | .GND | 43 | 9      | AGND |

|   | AI48 | 42 | 8      | AI49 |

|   | AI50 | 41 | 7      | AI51 |

|   | AI52 | 40 | 6      | AI53 |

|   | AI54 | 39 | 5      | AI55 |

|   | AI56 | 38 | 4      | A157 |

|   | AI58 | 37 | 3      | AI59 |

|   | AI60 | 36 | 2      | AI61 |

|   | AI62 | 35 | 1      | AI63 |

|   |      |    |        | 1    |

| Signal Name | Reference | Direction | Description                                  |

|-------------|-----------|-----------|----------------------------------------------|

| AI<015>     | AIGND     | Input     | Analog Input Channels 0                      |

|             |           |           | through 15. Each channel                     |

|             |           |           | pair, Al <i, i+1=""> (i = 0, 2,</i,>         |

|             |           |           | 414), can be configured                      |

|             |           |           | as either two single-ended                   |

|             |           |           | inputs or one differential input.            |

| AIGND       |           |           | Analog Input Ground. The                     |

| AIGIND      | -         | -         | three ground references                      |

|             |           |           | (AIGND, AOGND, and                           |

|             |           |           | DGND) are connected                          |

|             |           |           | together.                                    |

| AO0_REF     | AOGND     | Input     | Analog Output Channel 0/                     |

| AO1_REF     |           |           | 1 External Reference.                        |

| AO0_OUT     | AOGND     | Output    | Analog Output Channels                       |

| AO1_OUT     |           |           | 0/1                                          |

| AOGND       | -         | -         | Analog Output Ground.                        |

|             |           |           | The analog output volt-                      |

|             |           |           | ages are referenced to                       |

|             |           |           | these nodes. The three                       |

|             |           |           | ground references                            |

|             |           |           | (AIGND, AOGND, and DGND) are connected       |

|             |           |           | together.                                    |

| DI<015>     | DGND      | Input     | Digital Input channels.                      |

| DO<015>     | DGND      | Output    | Digital Output channels.                     |

| DGND        | DGND      | Output    | Digital Ground. This pin                     |

| DGND        | -         | -         | supplies the reference for                   |

|             |           |           | the digital channels at the                  |

|             |           |           | I/O connector as well as                     |

|             |           |           | the +5VDC supply. The                        |

|             |           |           | three ground references                      |

|             |           |           | (AIGND, AOGND, and                           |

|             |           |           | DGND) are connected                          |

|             |           |           | together.                                    |

| CNT0_CLK    | DGND      | Input     | Counter 0 Clock Input. The                   |

|             |           |           | clock input of counter 0                     |

|             |           |           | can be either external or                    |

|             |           |           | internal, as set by soft-<br>ware.           |

| CNT0_OUT    | DGND      | Output    | Counter 0 Output.                            |

| CNT0_GATE   | DGND      | Input     | Counter 0 Gate Control.                      |

| PACER OUT   | DGND      | Output    | Pacer Clock Output. This                     |

| I ACEN_OUT  | DGND      | Output    | pin pulses once for each                     |

|             |           |           | pacer clock when turned                      |

|             |           |           | on. If A/D conversion is in                  |

|             |           |           | the pacer trigger mode,                      |

|             |           |           | users can use this signal                    |

|             |           |           | as a synchronous signal                      |

|             |           |           | for other applications.                      |

| TRG_GATE    | DGND      | Input     | A/D External Trigger Gate.                   |

|             |           |           | When TRG _GATE is con-                       |

|             |           |           | nected to DGND, it will dis-                 |

|             |           |           | able the external trigger                    |

| EXT TRG     | DGND      | Innet     | signal to input.  A/D External Trigger. This |

| ENI_IKG     | שמאטע     | Input     | pin is external trigger. This                |

|             |           |           | nal input for the A/D con-                   |

|             |           |           | version. A low-to-high                       |

|             |           |           | edge triggers A/D conver-                    |

|             |           |           | sion to start.                               |

| +12V        | DGND      | Output    | +12 VDC Source.                              |

| +5V         | DGND      | Output    | +5 VDC Source.                               |

|             |           |           | l .                                          |

# **Signal Connections**

#### **Analog Input Connections**

#### **Single-ended Channel Connections**

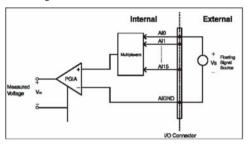

The single-ended input configuration has only one signal wire for each channel, and the measured voltage (Vm) is the voltage of the wire as referenced against the common ground.

Figure 1: Single-ended Channel Connections

#### Differential Channel Connections

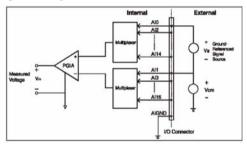

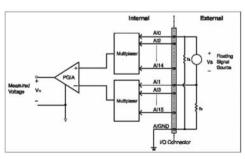

The differential input channels operate with two signal wires for each channel, and the voltage difference between both signal wires is measured. On PCI-1742U, when all channels are configured to differential input, up to 8 analog channels are available.

Figure 2: Differential Connection - Ground Signalt

Figure 3: Differential Connection - Floating Signal

#### **Analog Output Connections**

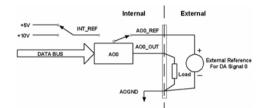

The PCI-1742U provides two D/A output channels, **AO0** and **AO1**. You may use the PCI-1742U internally-provided precision -5V (-10V) reference to generate 0 to +5 V (+10 V) D/A output range. You may also create a D/A output range through the external reference AO0\_REF. The external reference input range is +/-10 V. For example, connecting with an external reference of -7 V will generate 0 ~ +7 V D/A output.

Figure 4: Analog Output Connections

### **Trigger Source Connections**

#### **Internal Pacer Trigger Connection**

PCI-1742U includes one 82C54 compatible programmable Timer/Counter chip which provides three 16-bit counters connected to a 10 MHz clock, each designated specifically as Counter 0, Counter 1 and Counter 2. Counter 0 is a counter which counts events from an input channel or outputting pulse. Counter 1 and Counter 2 are cascaded to create a 32-bit timer for pacer triggering. A low-to-high edge from the Counter 2 output (PACER\_OUT) will trigger an A/D conversion on the PCI-1742U. At the same time, you can also use this signal as a synchronous signal for other applications.

#### **External Trigger Source Connection**

In addition to pacer triggering, the PCI-1742U also allows external triggering for A/D conversions. A low-to-high edge coming from **EXT\_TRG** will trigger an A/D conversion on the PCI-1742U. When **DGND** is connected to **TRG\_GATE**, the external trigger function is thereby disabled.